Symmetrical Gate Turn-Off Thyristor Type SA20AP1200UF

## Contact us!

Date: July, 2020 Data Sheet Issue: 1

| ORDERING INFORMATION |              |              |              | (Please quote 12 to 15 digit code as below) |              |               |  |

|----------------------|--------------|--------------|--------------|---------------------------------------------|--------------|---------------|--|

| SA                   | 20           | AP           | 1200         | U                                           | F            |               |  |

| -                    | Voltage Code | Outline Code | Current code | Type code                                   | Special code | Optional code |  |

Explore the full range of our semiconductor portfolio online

# SANCONA®

### **Absolute Maximum Ratings**

|                  | VOLTAGE RATINGS                                 | MAXIMUM<br>LIMITS | UNITS |

|------------------|-------------------------------------------------|-------------------|-------|

| V <sub>DRM</sub> | Repetitive peak off-state voltage, (note 1)     | 2000              | V     |

| V <sub>RSM</sub> | Non-repetitive peak off-state voltage, (note 1) | 2100              | V     |

| V <sub>RRM</sub> | Repetitive peak reverse voltage                 | 1400              | V     |

| V <sub>RSM</sub> | Non-repetitive peak reverse voltage             | 1400              | V     |

| note 1)          | $V_{GK} = -2V$                                  |                   |       |

|                       | OTHER RATINGS                                                                                           | MAXIMUM<br>LIMITS     | UNITS            |

|-----------------------|---------------------------------------------------------------------------------------------------------|-----------------------|------------------|

| I <sub>TGQ</sub>      | Peak turn-off current (note 1)                                                                          | 1200                  | А                |

| L <sub>S</sub>        | Snubber loop impedance, $I_{TM} = I_{TGQ}$ (note 1)                                                     | 0.3                   | μΗ               |

| I <sub>T(AV)M</sub>   | Mean on-state current, T <sub>sink</sub> = 55°C, (note 2)                                               | 670                   | А                |

| I <sub>T(RMS)</sub>   | Nominal RMS on-state current, T <sub>sink</sub> = 25°C (note 2)                                         | 1340                  | А                |

| I <sub>TSM</sub>      | Peak non-repetitive surge current t <sub>p</sub> = 10ms                                                 | 10.5                  | kA               |

| I <sub>TSM2</sub>     | Peak non-repetitive surge current (note 3)                                                              | 19                    | kA               |

| l <sup>2</sup> t      | $I^{2}t$ capacity for fusing $t_{p}$ = 10ms                                                             | 550 · 10 <sup>3</sup> | A <sup>2</sup> s |

| (di/dt) <sub>cr</sub> | Critical rate of rise of on-state current, (note 4)                                                     | 1000                  | A/µs             |

| P <sub>FGM</sub>      | Peak forward gate power                                                                                 | 210                   | W                |

| P <sub>RGM</sub>      | Peark reverse gate power                                                                                | 8                     | kW               |

| I <sub>FGM</sub>      | Peak forward gate current                                                                               | 140                   | А                |

| V <sub>RGM</sub>      | Peak reverse gate voltage (note 5)                                                                      | 18                    | V                |

| t <sub>off</sub>      | Minimum permissible off-time, $I_{TM} = I_{TGQ}$ (note 1)                                               | 80                    | μs               |

| t <sub>on</sub>       | Minimum permissible off-time                                                                            | 20                    | μs               |

| T <sub>jop</sub>      | Operating temperature range                                                                             | -40 to +125           | °C               |

| T <sub>stg</sub>      | Storage temperature range                                                                               | -40 to +150           | °C               |

| note 1)               | $T_j$ = 125°C, $V_D$ = 80% $V_{DM}$ , $V_{DM}$ ≤ $V_{DRM}$ , di <sub>GQ</sub> /dt = 20A/μs, $C_S$ = 3μF |                       |                  |

| note 2)               | Double-side cooled, single phase, 50Hz, 180° half-sinewave.                                             |                       |                  |

| note 3)               | Half-sinewave, t <sub>p</sub> = 2ms                                                                     |                       |                  |

| note 4)               | For di/dt > 1000A/µs please consult factory.                                                            |                       |                  |

| note 5)               | May exceed this value during turn-off avalanche period.                                                 |                       |                  |

# SANCONA®

### Characteristics

|                       | PARAMETER                                                                                                                                                    | TEST CONDITIONS                                                | MIN  | ТҮР  | МАХ   | UNITS |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|------|-------|-------|

| V <sub>TM</sub>       | Maximum peak on-state voltage                                                                                                                                | I <sub>G</sub> = 2A, I <sub>T</sub> = 1200A                    | -    | 3.0  | 3.3   | V     |

| IL                    | Latching current                                                                                                                                             | T <sub>i</sub> = 25°C                                          | -    | 15   | -     | А     |

| Ι <sub>Η</sub>        | Holding current                                                                                                                                              | 1j - 23 C                                                      | -    | 15   | -     | А     |

| (dv/dt) <sub>cr</sub> | Critical rate of rise of off-state voltage                                                                                                                   | $V_{\rm D}=80\% V_{\rm DRM}, V_{\rm GR}=-2V$                   | 1000 | -    | -     | V/µs  |

| I <sub>DRM</sub>      | Peak off-state current                                                                                                                                       | Rated $V_{DRM}$ , $V_{GR} = -2V$                               | -    | -    | 50    | mA    |

| I <sub>RRM</sub>      | Peak reverse current                                                                                                                                         | Rated V <sub>RRM</sub>                                         | -    | -    | 100   | mA    |

| I <sub>GKM</sub>      | Peak negative gate leakage current                                                                                                                           | $V_{GR} = -16V$                                                | -    | -    | 200   | mA    |

|                       |                                                                                                                                                              | $T_j$ = -40°C, $V_D$ = 25V, $R_L$ = 25m $\Omega$               | -    | 1.0  | -     | V     |

| V <sub>GT</sub>       | Gate trigger voltage                                                                                                                                         | $T_j = 25^{\circ}C$ , $V_D = 25V$ , $R_L = 25m\Omega$          | -    | 0.9  | -     | V     |

|                       |                                                                                                                                                              | $T_j = 125^{\circ}C, V_D = 25V, R_L = 25m\Omega$               | -    | 0.8  | -     | V     |

|                       |                                                                                                                                                              | $T_j = -40^{\circ}$ C, $V_D = 25$ V, $R_L = 25$ m $\Omega$     | -    | 3.0  | 8.0   | А     |

| I <sub>GT</sub>       | Gate trigger current                                                                                                                                         | $T_j = 25^{\circ}C$ , $V_D = 25V$ , $R_L = 25m\Omega$          | -    | 0.6  | 2.5   | А     |

|                       |                                                                                                                                                              | $T_j = 125^{\circ}C, V_D = 25V, R_L = 25m\Omega$               | -    | 60   | 500   | mA    |

| t <sub>d</sub>        | Delay time                                                                                                                                                   | (note 2)                                                       | -    | 1.0  | -     | μs    |

| t <sub>gt</sub>       | Turn-on time                                                                                                                                                 | Conditions as for $t_d, (10\% I_{GM} \mbox{ to } 10\% V_D)$    | -    | 3.0  | 7.0   | μs    |

| t <sub>f</sub>        | Fall time                                                                                                                                                    | (note 3)                                                       | -    | 0.8  | -     | μs    |

| t <sub>gq</sub>       | Turn-off time                                                                                                                                                | Conditions as for $t_f,(10\% I_{GQ} \text{ to } 10\% I_{TGQ})$ | -    | 12   | 13    | μs    |

| I <sub>GQ</sub>       | Turn-off gate current                                                                                                                                        | Conditions as for t <sub>f</sub>                               | -    | 250  | -     | А     |

| Q <sub>GQ</sub>       | Turn-off gate charge                                                                                                                                         |                                                                | -    | 1600 | 2000  | mC    |

| t <sub>tail</sub>     | Tail time                                                                                                                                                    | Conditions as for $t_{f},$ (10%I_{TGQ} to I_{TGQ} < 1A)        | -    | 40   | 60    | μs    |

| t <sub>gw</sub>       | Gate off-time (note 4)                                                                                                                                       | Conditions as for t <sub>f</sub>                               | 150  | -    | -     | μs    |

|                       |                                                                                                                                                              | Double side cooled                                             | -    | -    | 0.027 | K/W   |

| R <sub>thJK</sub>     | Thermal resistance, junction to sink                                                                                                                         | Cathode side cooled                                            | -    | -    | 0.070 | K/W   |

|                       |                                                                                                                                                              | Anode side cooled                                              | -    | -    | 0.045 | K/W   |

| F                     | Mounting force                                                                                                                                               | (note 5)                                                       | 15   | -    | 25    | kN    |

| Wt                    | Weight                                                                                                                                                       |                                                                | -    | 480  | -     | g     |

| note 1)               | Unless otherwise indicated T <sub>j</sub> = 125°C                                                                                                            |                                                                |      |      |       |       |

| note 2)               | $V_D = 50\% V_{DRM}$ , $I_{TGQ} = 1200A$ , $I_{GM} = 40A$ , $di_G/dt = 20A/\mu s$ , $T_j = 25^{\circ}C$ , $di/dt = 300A/\mu s$ , $(10\% I_{GM} to 90\% V_D)$ |                                                                |      |      |       |       |

| note 3)               | $V_D = 80\% V_{DRM}$ , $I_{TGQ} = 1200A$ , $C_S = 3\mu$ F, $di_G/dt = 40A/\mu s$ , $V_{GR} = -16V$ , (90% $I_{TGQ}$ to 10% $V_D$ )                           |                                                                |      |      |       |       |

| note 4)               | The gate off-time is the period during which the gate circuit is required to remain low impedance to allow for the pas-<br>sage of tail current.             |                                                                |      |      |       |       |

| note 5)               | For other clamping forces, consult factory.                                                                                                                  |                                                                |      |      |       |       |

## Request full technical data sheet via e-mail, free of charge:

## **Order Now!**

## **SANCONA**<sup>®</sup>

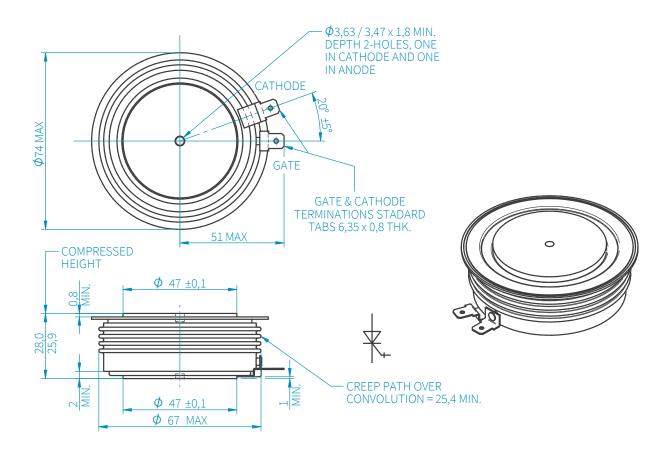

### **Outline Drawing**

#### **SANCONA GmbH**

An der Hebemärchte 26 D-04316 Leipzig // Registry Court: Leipzig HRB 32946

VAT Reg No.: DE308741810

Tax number: 232/118/085686

The information contained herein is confidential and is protected by Copyright. The information may not be used or disclosed except with written permission of and in the manner permitted by the proprietors SANCONA GmbH. In the interest of product improvement, SANCONA reserves the right to change specifications at any time without prior notice. Devices with a suffix code (2-letter, 3-letter or letter/digit/letter combination) added to their generic code are not necessarily subject to the conditions and limits contained in this report.

©SANCONA GmbH